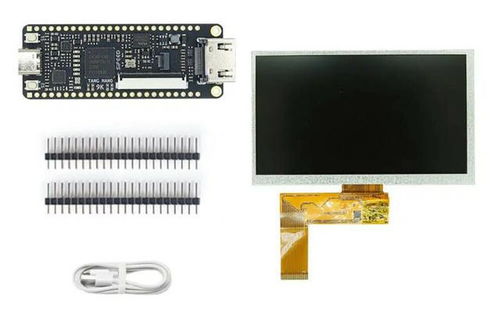

Tang Nano 9K FPGA开发板 构建全集成PicoRV32 RISC-V软核系统的理想平台

Tang Nano 9K是一款基于高云半导体小蜜蜂系列GW1NR-LV9 FPGA芯片的高性价比、入门级开发板。其丰富的逻辑资源(约8640个LUT4)、嵌入式块状RAM(B-SRAM)和灵活的I/O,使其成为在单芯片上实现并运行完整PicoRV32 RISC-V软核及其外围硬件系统的绝佳选择。

一、核心优势:为何选择Tang Nano 9K?

- 充足的逻辑资源:GW1NR-LV9 FPGA提供了足够的可编程逻辑单元,能够轻松容纳PicoRV32这样的精简RISC-V内核(通常仅需1000-2000个LUTs),并为后续扩展复杂的自定义外设或加速器预留了广阔空间。

- 集成存储与PLL:板载的嵌入式存储块可用于实现软核的指令与数据存储器(如RAM或ROM),而片内锁相环(PLL)则能生成系统所需的各种时钟频率,确保了系统的高效与稳定运行。

- 丰富的外设接口:开发板自带RGB LED、按键、用户IO扩展接口、SPI Flash(用于存储FPGA配置文件和软核程序)等,为连接和模拟各类外设提供了硬件基础。

二、系统设计:模拟PicoRV32软核与完整外设生态

在Tang Nano 9K上构建一个完整的微处理器系统,通常包含以下核心模块,全部通过硬件描述语言(如Verilog)设计并集成:

- PicoRV32 RISC-V CPU软核:作为系统的中央处理器。这是一个高度可配置、最小化的32位RISC-V实现,支持RV32IMC指令集。设计时需将其作为一个模块实例化,并连接至系统总线。

- 片上存储器系统:

- 指令存储器(IMEM):通常使用FPGA的块RAM实现,用于存储CPU执行的程序代码。

- 数据存储器(DMEM):同样使用块RAM,作为CPU运行时的工作RAM。

- 内存映射:设计一个地址解码器,为不同的外设(如UART、GPIO、定时器)分配唯一的地址空间。

- 系统总线:通常采用简单的Wishbone或AXI4-Lite等总线协议,作为CPU与所有外设之间通信的标准化通道,实现模块化的设计。

- 关键外设IP核(硬件设计):

- 通用异步收发器(UART):用于与PC进行串行通信,是调试和输入输出的关键。

- 通用输入输出(GPIO):控制板载LED、读取按键状态,并连接外部扩展设备。

- 系统定时器(Timer):提供精确的时间基准,用于任务调度、延时等。

- SPI控制器:用于读写板载SPI Flash,可以实现“程序存储于Flash、上电后加载至RAM运行”的典型嵌入式工作流程。

- 脉冲宽度调制(PWM):可用于控制LED亮度或电机速度。

三、开发流程与工具链

- 硬件设计与综合:使用高云云源软件(Gowin EDA)进行Verilog编码、综合、布局布线和生成比特流文件。将PicoRV32源码与自编写的外设模块一同集成到顶层设计中。

- 软件程序开发:利用RISC-V GNU工具链(如riscv-gcc)编写C/C++应用程序。通过链接脚本,将程序代码定位到设计好的存储器地址空间中。

- 系统集成与调试:

- 将编译好的软件程序(.bin或.hex文件)初始化到FPGA设计中的ROM/BRAM里,或通过UART引导加载。

- 通过Gowin EDA的逻辑分析仪工具进行内部信号抓取调试。

- 最终将完整的比特流文件下载到Tang Nano 9K的SPI Flash中,实现上电自启动运行。

四、应用与展望

成功在Tang Nano 9K上运行PicoRV32及全套外设,标志着一个真正意义上的片上系统(SoC)的实现。开发者可以在此基础上:

- 深入学习计算机体系结构:理解CPU、总线、存储与外设如何协同工作。

- 进行嵌入式开发实践:编写驱动程序,控制各种硬件。

- 实现定制化加速:利用富余的FPGA资源,为PicoRV32添加专用的硬件加速引擎(如算法加速器),探索软硬件协同设计的魅力。

Tang Nano 9K以其亲民的价格和恰到好处的资源,为FPGA和RISC-V爱好者提供了一个从零开始搭建并理解一个完整、可实际运行的计算系统的完美沙盒。通过将PicoRV32软核与所有必需的外设硬件集成于一体,开发者能够获得从底层硬件到上层软件的端到端设计体验。

如若转载,请注明出处:http://www.seo1zz.com/product/59.html

更新时间:2026-01-12 14:29:08